#问题描述

无论多小的block/cell,使用calibre DRC的waiver功能都无法waive任何DRC,调入waived gds都没任何反应。

calibre版本:2021.4_33.16

#解决办法

把block/cell重命名个短点的名字。

这应该是calibre的一个bug,无论2020还是2021版都有这个问题。

on going

无论多小的block/cell,使用calibre DRC的waiver功能都无法waive任何DRC,调入waived gds都没任何反应。

calibre版本:2021.4_33.16

把block/cell重命名个短点的名字。

这应该是calibre的一个bug,无论2020还是2021版都有这个问题。

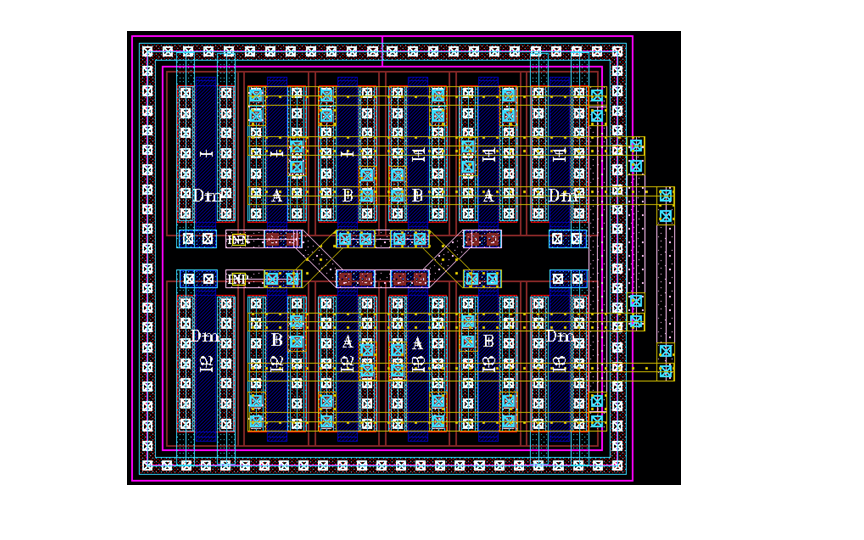

因为相通图层之间不同的距离,导致刻蚀速率不同。简单举例来说,把一根length=1um的poly放在一大片空旷地带(周围没有其他poly),最后这根poly的有效length可能只有0.99um。这在一些模拟版图中可能会导致mismatch,所以一般会被要求在需要匹配的器件两边甚至周围加上dummy以减少mismatch。

一般在模拟版图中,为了减少mismatch,会被要求在matching-transistor周围加上dummy

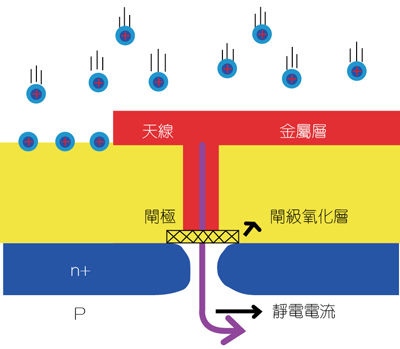

天线效应的产生粗略的讲就是金属表面积累的电荷过多,但又无法形成对地的放电通路,结果很有可能是对栅氧造成破坏。由于现代工艺尺寸越来越先进,沟道长度越来越小,antena的问题就越来越受重视。通常,我们通过金属跳线或者在poly-gate旁边放置足够面积的diode可以避免天线效应的发生。但是金属该往上跳还是往下跳呢?

我们都知道做mask的时候是从低层往高层做的。每一道工序都有诸如平坦化,隔离等,之后肯定会有静电泄放的操作。从这个角度来说,假如metal3过大有antena的问题,我们用metal4对其跳线。在做metal3的mask时,metal3实际上分开的,只有做到metal4的时候他们才会连起来,而到metal4时,metal3的表面电荷已经由于工艺过程减少很多了;而如果用metal2对其跳线,在做metal3时,metal2和metal3是会相连的,并没有起到减少电荷的作用。

栅氧漏电,尽管对功耗不利,但对天线效应是有利的。栅氧漏电可以防止电荷积累达到击穿。所以,实际上可以看到薄的栅氧较厚栅氧不易发生损坏,因为当栅氧变薄,漏电是指数上升的,而击穿电压是线性下降的。

一般来说command file会定义检查是否antena metal连到gate-poly上,还有是否面积过大。解决方法我建议是在靠近gate-poly的地方断开metal用高层metal跳一下,当然这在drc中可能不太好查,所以drc一般规定在发生antena的metal上有一个N-diode,越靠近transistor越好。